# Zero Defects

Entegris Newsletter

### CONTENTS

### 1. Entegris News

- Entegris Completes Acquisition of SAES Pure Gas Business from SAES Group

- Entegris Presents at UCPSS

#### 2. Yield Improvement

- Reducing Contamination Points in Clean Chemical Delivery from Manufacture through Point of Use

- Bowling for Contaminants: The New Science of Gas Purification

- Considerations for Improving 3D NAND Performance, Reliability, and Yield

#### 6. Innovation

Ammonia Sorption/Outgassing Ability of Entegris FOUPs Evaluation and its Volatile Acids Comparison

### 9. Product Highlight

AccuSizer Mini Used for Online Particle Size Analysis of CMP Slurries Around the World

### **ENTEGRIS EUROPE**

A question about Entegris products? Call your customer service center

France T +33 (0)4 76 35 73 50 F +33 (0)4 76 35 73 80

Germany T +49 (0)351 795 97-0 F +49 (0)351 795 97-498

Israel T +972 (0)73 221 0000 F +972 (0)73 221 0030

A question about cleaning services? Call Entegris Cleaning Process ECP

T +33 (0)4 67 22 40 95 F +33 (0)4 67 22 49 90

### www.entegris.com

Publisher: Entegris Europe Editor: Françoise Moign Contact francoise.moign@entegris.com for permission to reproduce Zero Defects articles

### Entegris Completes Acquisition of SAES Pure Gas Business from SAES Group

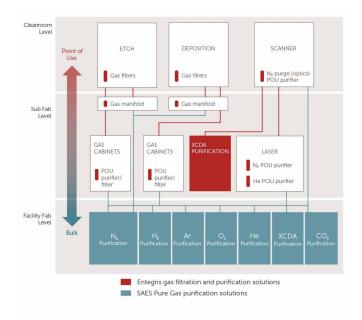

Entegris announced on June 25 the acquisition completion of the SAES Pure Gas business from SAES Getters S.p.A. ("SAES Group"), an advanced functional materials company headquartered in Milan, Italy. The SAES Pure Gas business, a leading provider of high-capacity gas purification systems used in semiconductor manufacturing and adjacent markets is based in San Luis Obispo, California and will report into the Microcontamination Control division of Entegris.

Under the agreement, which was originally announced on June 6, 2018, Entegris has purchased the shares and assets which comprise the SAES Pure Gas business for approximately \$355 million, subject to customary purchase price adjustments.

Materials purity plays an increasingly critical role in the performance and reliability of advanced semiconductors as the sensitivity to contamination approaches the parts per quadrillion level. Advanced memory devices require significantly higher gas consumption per processed wafer to support shrinking geometries and multi-layer device architectures. As a result of this height-ened sensitivity to molecular contamination and increased gas consumption, semiconductor manufacturers are depending on bulk gas suppliers to deliver process gases that meet new purity requirements.

"As we executed our evolutionary strategy for SAES Group and considered potential acquirers for the SAES Pure Gas business, we viewed Entegris as the ideal partner given its leadership in the semiconductor industry, the complementary nature of its filtration and purification offerings, and its financial and operational strengths," said Massimo della Porta, president of SAES Getters S.p.A.

"With this acquisition, we are even better positioned to meet the increasingly more stringent contamination control requirements within the semiconductor industry," said Bertrand Loy, president and Chief Executive Officer of Entegris. "The combination of technology platforms and talent will help us create superior value for our customers and shareholders."

### Entegris Presents at UCPSS

Join us September 2-5 in Leuven, Belgium, at <u>UCPSS</u>; the conference devoted to cleaning and surface preparation for micro and nanotechnology electronic applications and related fields.

Entegris presents:

- Post-CMP cleaners for tungsten advanced nodes: 10 nm and 7 nm

- Determination of HCl transport coefficients of real FOUP polymers for HCl FOUP-to-wafer crosscontamination assessment\*

Please refer to this <u>link</u> for presentation dates and times.

\*Study done in collaboration with CEA TECH

## Reducing Contamination Points in Clean Chemical Delivery from Manufacture through Point of Use

### White Paper Entegris Inc.

As mega-trends, such as artificial intelligence and robotics, smart homes and smart cars, and the Internet of things evolve to meet growing needs for speed, scale, and reliability, they force integrated circuit (IC) manufacturers to increase processor power efficiency and memory size. At the same time, device manufacturers striving to meet new worldwide consumer and business data demands at lower costs, face significant challenges in terms of process control, yield, and economics.

As logic devices migrate to smaller line widths, 3D NAND architectures increase layers, and DRAM memory density increases, sensitivity to contamination and defects have a greater impact on device performance. To achieve optimum wafer yield and reliability, the microelectronics industry needs to address the increased materials consumption requirements and the material purity challenges for these high-performance technologies from chemical manufacture to their point of use.

*Next generation semiconductor manufacturing purity levels are approaching parts per quadrillion (ppq).*

### CHALLENGES

Controlling contamination begins with the chemicals that come into direct contact with every wafer. **Increasing chem**ical purity is the first step in enabling process cleanliness and improving device yield. This is why device manufacturers continue to pressure chemical suppliers to deliver a higher level of purity, soon approaching parts per quadrillion (ppq), and avoid introducing contaminants during chemical packaging, transport, and distribution. Equally important are material purity and the materials of construction in fluid delivery systems. Without contamination-controlled chemical packaging, filtration, pumps, and fluid handling components, chemicals are vulnerable to recontamination by particles, metals, and impurities.

Conducting contamination mapping to understand the contamination source is critical to defect control, yet it can be especially challenging when manufacturers source products with varying cleanliness levels and combine batches from many different vendors.

Understanding operations and sources of contamination to develop materials-enabled solutions that ensure the integrity of processes to control contamination begins with the chemicals that come into direct contact with every wafer; increasing chemical purity is the first step in enabling process cleanliness and improving device yield. From raw materials, to internal processes, to fluid handling systems, Entegris delivers a higher level of purity and takes care to avoid introducing contaminants during chemical packaging, transport, and distribution.

# ENTEGRIS SOLUTIONS FOR ACHIEVING CLEAN CHEMICAL DELIVERY FROM MANUFACTURE THROUGH POINT OF USE

Entegris is in a unique position to help customers maintain a clean chemical delivery environment with contaminationcontrolled chemical packaging, filtration, pumps, and fluid handling products that will increase product yield and reduce contamination of process chemicals.

For an ideal partnership, it's imperative to understand the unique challenges of clean chemical delivery and work with customers to develop and optimize operations by identifying potential sources of contamination and the solutions that remove particle and metal impurities. From safe and efficient chemical storage and delivery systems to a broad range of fluid handling products to expertise in filtration and purification technology, passion for purity leads to integrity of processes and helps increase yield.

To learn more, download the full white paper, "Reducing Contamination Points in Clean Chemical Delivery from Manufacture through Point of Use" at www.entegris.com/ccd.

## Bowling for Contaminants: The New Science of Gas Purification

White Paper Entegris Inc.

Purity of gases and chemicals has always played a critical role in the performance and reliability of advanced semiconductors and memory devices. Over the past few years, fab-cleanroom purity requirements themselves have changed exponentially in key process areas and are now approaching parts per quadrillion.

To remain competitive, many semiconductor manufacturers have increased manufacturing volumes which subsequently increases the overall consumption of gases. In addition to increased volumes, both logic and advanced memory devices require significantly higher gas consumption per processed wafer to support shrinking geometries and multi-layer device architectures such as finFETS and 3D NAND. For example, the move from 20 nm logic to 7 nm logic doubled the number of process steps. As a result, process gas consumption is expected to increase over the next five years.

Concurrently, the industry is looking to achieve higher density at lower power which also increases the complexity of the processes.<sup>1</sup>

These additional process steps impact yields as there are more opportunities to expose wafers to process excursions. Even trace contaminants in the gas supply can cause measurable shifts that affect chip performance by interacting with a process, potentially costing the manufacturer thousands or even millions of dollars.<sup>2</sup>

### WHAT DO CONTAMINANTS LOOK LIKE?

Contaminants in both bulk and specialty gas supplies come in several forms. Categorized as particulates or molecular contaminants, even historically benign contaminants have become problematic and can cause defects in today's 7 nm node devices or 3D NAND structures.

| Contaminant type                                                      | Standard surrogate                                    | Typical impurity<br>levels (outlet purity) |

|-----------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------|

| Acids<br>NO <sub>x</sub> , SO <sub>x</sub> , Organic acids            | SO <sub>2</sub>                                       | 0.1-1 ppmV (<1 pptV)                       |

| Atmospherics<br>CO <sub>2</sub> , CO, O <sub>2</sub> , N <sub>2</sub> | CO <sub>2</sub> , CO, O <sub>2</sub> , N <sub>2</sub> | 0.1-1.0 ppmV (<100<br>pptV)                |

| Bases<br>Amines, organoamines, silazanes                              | Ammonia (NH <sub>3</sub> )                            | 1-100 ppbV (<1 ppbV)                       |

| Metals<br>Fe, Mn, Mo, Ni, Cr, others                                  | E34 list, Fe, Cr                                      | 1-100 ppbV (<1 ppbV)                       |

| Moisture                                                              | H <sub>2</sub> O                                      | 0.1-25 ppmV (<1 ppbV)                      |

| Organics<br>Condensable (45-100 amu;<br>butane; IPA, toluene)         | Toluene Decane                                        | 0.1-2 ppmV (<1 pptV)                       |

| Non-Condensable (>100 amu;<br>decane)                                 |                                                       |                                            |

| Refractory compounds<br>Halogen-containing HCs, silicon<br>compounds  | HMDSO                                                 | <100 ppbV (<1 pptV)                        |

### **END TO END SOLUTION**

As a result of this heightened sensitivity to molecular contamination and increased gas consumption, semiconductor manufacturers are placing new requirements on suppliers of both bulk and specialty gases to deliver process gases customized to meet purity requirements. This article explains the importance of applying purification science to managing the gas supply purity from the source throughout all the wafer process steps to ensure the highest device yield.

To learn more, visit the Entegris End to End Gas Purity page at <u>https://www.entegris.com/content/en/pure/</u> <u>gas-purification-solutions.html</u>

#### REFERENCES

- 1. A Tolla, PhD, "Larger Fabs + Smaller Devices = More Gases," August 6, 2015 http://semimd.com/materials-matters/2015/08/06/larger-fabs-smallerdevic-es-more-gases/

- A Tolla, PhD, "Fabs Seeking Higher Quality Electronic Materials to Meet Technology Demands" August 27, 2015 SemiMD,<u>http://semimd.com/</u> materials-matters/2015/08/27/fabs-seeking-higher-quality-electronicmaterials-to-meet-technology-demands/

# Considerations for Improving 3D NAND Performance, Reliability, and Yield

### White Paper Entegris Inc.

NAND flash technology has provided the world with nonvolatile memory capability for many years. Its uses have grown from flash drives to applications in laptops, smartphones, tablets, and solid-state devices now used in cloud storage operations. Over time, its structures have changed to meet growing needs for storage capacity, scale, and reliability demands, but the technology has proven its worth by delivering increased performance and lower power consumption with the promise of lower cost per bit than previous solid-state memory technologies.

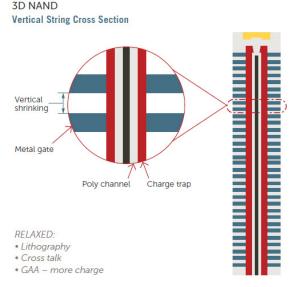

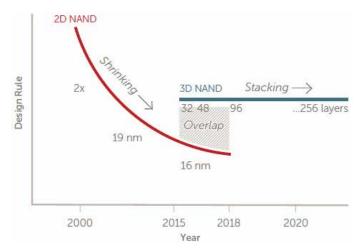

2D/planar NAND flash memory reached its scaling limit at the 15 nm mode. This forced manufacturers to adopt a revolutionary approach of stacking gate-all-around NAND cell layers to achieve new performance targets. This was the dawn of today's 3D NAND structures, which represent a fundamental shift in the approach to scaling. Instead of scaling horizontally on a two-dimensional plane, this technology introduced vertical scaling, or growth in a third dimension, see Figure 1. The promise of 3D NAND is higher density and a lower cost per bit.

*Fig. 1: The 3D NAND design stacks memory cells vertically in multiple layers to address 2D NAND scaling challenges, and to enable higher densities at lower cost per bit.*

With all its promising advantages, however, the process complexity and capital intensity of 3D NAND manufacturing add to the challenges fabs are facing in terms of process control, yield, and economics.<sup>1</sup> With heavy investments, manufacturing processes for 24-layer, 32-layer, and 48-layer 3D NAND were developed in the hope of realizing competitive cost-per-bit. By many accounts, 64-layer and higher 3D NAND structures appear to be where the highest potential for cost savings occurs.

Fig. 2: By stacking memory cells, 3D NAND architecture does not depend on lateral scaling to increase memory density

As 3D NAND races toward maturity and becomes a mainstream technology, chipmakers know there is still more to achieve to meet worldwide consumer and business data demands at lower costs, given the extreme complexities involved. Key areas that are worthy of addressing now are etch and deposition challenges and contamination issues.

# OPTIMIZE HIGH-ASPECT-RATIO ETCHING THROUGH MATERIALS DEVELOPMENT

In planar NAND technology, scaling is driven mostly by lithography. In scaling 3D NAND, extreme precision and process repeatability is required to create complex 3D structures with very high-aspect-ratio (HAR) features. Therefore, achieving success with 3D NAND requires innovative patterning solutions that minimize variability.<sup>1</sup>

Since the cell stack comprises stacked pairs of silicon nitride  $(Si_3N_4)$  at the cell level and silicon dioxide  $(SiO_2)$  to isolate the cells, it is extremely difficult for dry etch engineers to achieve a continuous and straight profile while maintaining high enough selectivity to the amorphous carbon hard mask to reach the bottom of the structure. As multilayer stack heights increase, so does the difficulty in achieving consistent etch and deposition profiles at the top and bottom of the memory array. For example, given a ratio of ~60:1, the selective removal of Si<sub>3</sub>N<sub>4</sub> in a memory stack becomes a wet-etch challenge. The difficulty is removing Si<sub>3</sub>N<sub>4</sub> consistently at the top and bottom of the stack and across the wafer, without etching any of the SiO<sub>2</sub>. Below 96 layers, this task is performed using hot phosphoric acid (~160°C); however, at 96 layers and above, a specially formulated wet etch chemistry is needed to improve process margin.

While dry etch tool and process innovations are required, the HAR features called for by 3D NAND, the hard mask, and subsequent materials-driving steps will also require development measures to bring stability, repeatability, and optimization to critical etch processes

### **ELIMINATE THE SLOWDOWN**

With 3D NAND, as the stack gets taller, the silicon channel gets longer, and the speed of the device becomes limited by the mobility of electrons in the channel and the increased lengths they must travel. Manufacturers will be able to compensate for this slowdown by increasing the mobility of the electrons in the silicon channel with the help of dopant species in the conductive silicon channel. Germanium doping is one known method for improving electron mobility and is currently in development for 3D NAND processing. The requirement is to achieve uniform doping along an HAR silicon channel approximately 50 nm in diameter and several microns deep. Suppliers are working to find a more efficient means of providing germanium dopants for this application. A promising approach may be to replace the current practice of supplying germane diluted in hydrogen with a process that uses pure germane. The objective is to look for the best option to maximize the conductivity of the channel and preserve the operational speed of the device.

### ESTABLISH DEFECT CONTROLS EARLY IN THE SUPPLY CHAIN

Process purity and defect controls are critical in 3D NAND processes. As the number of transistors increases in a 3D stack, one defect could block more than one cell and affect the performance of the entire device. Consequently, all potential contamination areas must be identified and proper steps taken to avoid defects stemming from sources like etch chambers, material impurities, inadequate chemical filtration, wafer carrier devices, and photoresist bubble formation.

In extreme HAR plasma etch steps, internal etch chamber parts are exposed to long, high-powered, and hightemperature processing and subject to erosion and particle shedding. To protect etch chamber parts against the aggressive plasma, a high-quality yttrium oxide ( $Y_2O_3$ ) layer deposited by techniques like physical vapor deposition (PVD) or plasma-enhances chemical vapor deposition (CVD) is required. The higher density and smoother surface of this layer results in fewer wafer defects.

The same is true for ALD process. Since ALD processes deposit the cell layers whose job it is to manage charge, they are highly sensitive to any source of contamination. Any surface that contacts the precursor is a potential source of contamination. The delivery system, pipe, valves, and gauges, have internal parts that may require protection from contamination by coating techniques. Parts coating is a highly tailored process. In some cases, PVD is sufficient, while ALD processing is used for parts requiring extreme step coverage. This greater attention to the quality of etch and deposition chamber parts, although initially driven by 3D NAND specifications, is increasingly demanded from high-end logic integrated device manufacturers (IDMs).

Current and ongoing advances in contamination control are critical to achieving the process-purity levels required to help enable increased layers and dimension shrinkage for advanced chip development. To maximize the purity potential, the entire semiconductor ecosystem must work together to identify potential contamination sources and develop suitable solutions

### SUMMARY

As process shrinking reached the scaling limit in 2D planar NAND flash memory, and technology advanced to stacking NAND cell layers in 3D, a new set of process challenges related to stacking rather than shrinking emerged. Addressing these challenges is leading to innovations in:

- Extreme HAR etching, including all peripheral innovations of hark mask and byproduct management

- Addressing needs in advanced contamination control to reduce defects

- Boosting electron mobility and conductivity to address

slowdown issues

- Solutions to precisely construct memory cells in extreme geometries

Closer collaborations between integrated device manufacturers, original equipment manufacturers, and materials makers/ contamination experts across the supply chain will allow process innovations that continue to enable 3D NAND into the fore-seeable future. With vertical cell stacking architecture clearly moving toward 128, 256, and perhaps beyond, the industry will achieve higher-performing, more reliable devices with greater capacity and lower cost per bit.

To read the full paper, visit Entegris website at <u>www.entegris.com/3dnand</u>

### REFERENCES

1. Overcoming Challenges in 3D NAND Volume Manufacturing, Solid State Technology website: <u>http://www.businesskorea.co.kr/english/news/</u> ict/20216-signaling-end-flat-nand-flash-era-percentage-3d-nandflash-production-exceeds-80

# Ammonia Sorption/Outgassing Ability of Entegris FOUPs Evaluation and its Volatile Acids Comparison

### By Paola GONZALEZ-AGUIRRE Ph.D., Engineer II, CEA/LETI assignee Entegris Inc.

In semiconductor manufacturing with decreasing geometries, the importance of chemical contamination control increases. AMC monitoring and control is as important as particle contamination but more difficult to detect. The level of basic impurities in the air can be critical; chemicals such as ammonia can have a detrimental effect on the photolithography process. A core technology, DUV photolithography, has been improved dramatically and requires shorter wavelength light. This technology has shown an increasing sensitivity to basic contamination, and ammonia has been rapidly identified as the dominant substance among airborne molecular contaminants. Wafers exposed to ammonia are at risk for structural defects such as: T-topping chemically amplified photoresist, incorrect imprinted line width, short-circuits, metal surface corrosion on the wafer, haze on wafers, degradation of HEPA/ULPA filter media, and haze on equipment optics.

Ammonia contamination comes from many sources within the cleanroom such as staff members and several production processes that may generate large quantities of ammonia, including chemical reactions between priming agents, cleaners, polishing materials, and Si-wafers. Despite the well-known effects of molecular bases, no report of cross contamination between FOUPs and wafers were found in this study. In a well-controlled fab environment, the amount of ammonia is generally very low in the cleanroom and processing equipment, and especially inside the FOUP. Nevertheless, fabs are challenged with cleaning ammonia contamination from FOUPs. To combat ammonia cross contamination, one needs to fully understand ammonia sorption/outgassing dynamics in FOUPs. The purpose of this paper is the assessment of two FOUP models in terms of potential (empty FOUP) and effective (wafer exposure) cross-contamination risks to wafers in order to address the most suitable handling solution (FOUP polymers).

### **EXPERIMENTAL**

Two different Entegris FOUPs were used: "PC" (a Spectra<sup>™</sup> FOUP made with ultrapure polycarbonate (PC) and "EBM/CNT" (an A300 FOUP made with Entegris Barrier Material (EBM) with carbon-nanotubes (CNT)).

FOUPs were first conditioned at cleanroom conditions (21°  $\pm$  2°C, 45  $\pm$  5% RH). A 10-µL NH<sub>3</sub> 2.9% solution droplet was used to contaminate the FOUP; similar protocol was used with HF and HCl solutions (2% and 3.7% respectively). Upon evaporation (door closed), this yields contamination of a few ppmv inside the FOUPs (14.74 ppmv NH<sub>3</sub>, 11.23 ppmv HF and 11.6 ppmv HCl), simulating a contamination event. 4 hours after the intentional contamination, and to avoid a considerable

airborne disturbance, an airborne sample was taken via impinger (1 L/min) for 2 minutes and analyzed by ionic chromatography (IC). After 24 hours of intentional contamination, most of the initial concentration has been sorbed by the inner FOUP surfaces. Next, the FOUPs were opened and the internal atmosphere was thoroughly purged with the help of a N<sub>2</sub> spray gun. The outgassing phase starts when the FOUP is closed. The airborne concentration was monitored for one week using air bubbling sampling (1 L/min during 5 minutes) and IC analysis.

### RESULTS

### \_\_\_\_

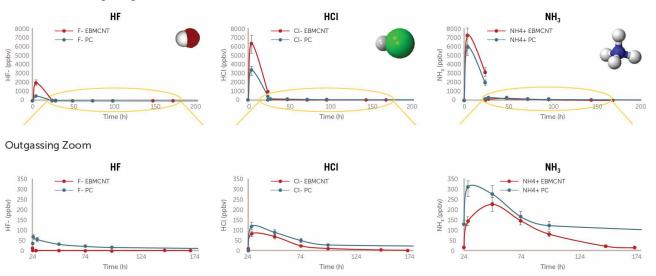

The contamination phase leads to a similar contamination FOUP material sorption ability ranking for ammonia as for both HF and HCl: EBM/CNT < PC. Diffusion of the contaminant into the polymer FOUP is responsible for the sorption ability, and the results for the three contaminants clearly demonstrate the barrier character of EBM/CNT polymer. Since the airborne concentrations of the ammonia case in both FOUP polymers remain markedly higher than in the HF and HCl cases, the major difference in the contaminant sorption ability ranking (NH<sub>3</sub> < HCl < HF) lies in the relative molecular penetration kinetics.

The outgassing phase shows two steps; first just after purge, an increase of contaminant levels in FOUPs was observed showing the outgassing from FOUP polymers (except for HF in EBM/ CNT, where no HF is detected with LLD of 0.62 ppbv). This behavior is due to a reverse molecular diffusion. Indeed, we consider that purge desorbs molecules at the polymer surface, and this leads to a strong inverse concentration gradient of contaminants into the polymer that promotes molecular diffusion from the core to the surface, resulting in contaminant outgassing. In the specific case of ammonia, the strong outgassing after purge in the EBM/CNT polymer is detected 4 hours after purge; corroborating the assumption that contaminant diffusion in EBM/CNT polymer is lower than diffusion in PC polymer.

continued on the next page

Contamination/Outgassing

Fig. 1: Contamination monitoring levels (ppbv) in FOUPs atmosphere during contamination phase and zoom zone of the airborne contaminant monitoring levels during outgassing phase for PC FOUPs & EBMCNT FOUPs

The second step in the outgassing phase is a slow decrease, following by a slow balance between polymers and airborne concentrations. Indeed, this slow diffusion process continues throughout the thickness of the polymer wall to reach a concentration gradient near the surface close to zero. As a result, contaminant levels at the polymer surface and in the FOUP atmosphere decrease to achieve stable amounts. NH3 outgassing is higher than HCl and HF. Solubility is the outgassing phenomena driving force. Results suggest that small molecules as HF (Van der Waals volume 15.77A<sup>3</sup>) [8] have larger solubility, compared to HCl and NH<sub>3</sub> (22.45 A<sup>3</sup> and 22.86 A<sup>3</sup> respectively). Likewise, the HCl linear configuration allows major solubility compared to an ammonia tetrahedral configuration. Given that, we assume that if a wafer surface presenting similar contamination affinity the FOUP-to-wafer contamination transfer expected will follow NH<sub>3</sub> < HCl < HF and PC > EBM/CNT.

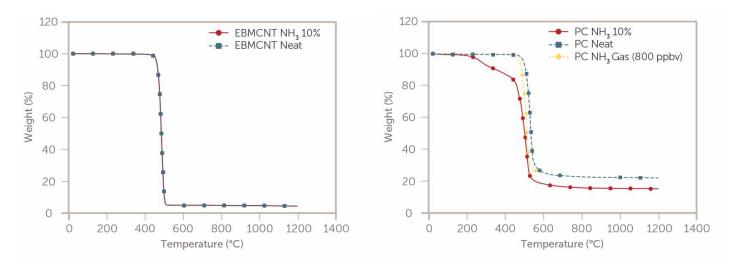

Ammonia reactivity in PC is well known. In order to explore the potential impact of ammonia in PC FOUPs, a thin films (< 100  $\mu$ m) samples of PC and EBMCNT polymers were immersed in 20 mL of NH<sub>3</sub> 10% solution overnight and analyzed by TGA EBM/CNT polymer does not present any physical or thermal change, meanwhile the PC polymer film became brittle and thermogravimetrical results show a clear PC degradation. As submerging the PC thin film in NH<sub>3</sub> 10% is a drastic measure and FOUPs are never under this hard condition, another thin film PC sample was introduced into a reactor under 800 ppbv of ammonia gas (RH 40%) flow for 200 hours. These low ammonia contamination conditions are enough to promote PC degradation.

Fig. 2: TGA results for EBMCNT and PC thin films before and after NH3 10% solution immersion and gaseous NH3 800ppbv exposure

### CONCLUSION

Comparative study results allow us to identify the best FOUP platform with respect to NH<sub>3</sub>, HF, HCl cross contamination. The contamination phase in both polymers (function of diffusion and solubility) present the same contaminant ranking affinity, NH<sub>3</sub> < HCl < HF. For the outgassing phase in the both polymers (mainly solubility dependent) contaminant release follows NH<sub>3</sub> > HCl > HF. With these results, one can establish that ammonia solubility is lower than HCl and much lower than HF.

The FOUP rankings obtained by the contaminant airborne concentration measurements (empty FOUP) pointed EBM/CNT FOUPs as the best minienvironment to control these AMCs. One can therefore conclude that actual contaminant transfer from the FOUP to a wafer substrate is strongly related to the dose released by the polymer (PC >> EBM/CNT), and that the use of FOUPs made of barrier materials such as EBM/CNT enable excellent control of very low moisture and volatile acids as well as ammonia cross-contamination. Finally, due to its reactivity, PC FOUPs are not suitable in environments containing ammonia.

## AccuSizer Mini Used for Online Particle Size Analysis of CMP Slurries Around the World

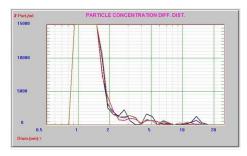

Chemical Mechanical Planarization (CMP) is widely used in the semiconductor industry to smooth surfaces. The particle size distribution of the polishing slurry is critical to controlling the success of the planarization process. It is the largest particles or LPC's that can scratch wafers or lead to other excursions. In terms of preserving yield, it is important to monitor LPC's in slurries. Monitoring online provides even better ROI as excursions are detected sooner. Entegris offers a solution, the AccuSizer Mini Online slurry monitor. The Accusizer Mini counts and sizes particles in the range of 0.15 to 400 microns. Almost all types of slurries can be monitored using a modular approach that combines the autodilution fluidics with different sensors.

Fig. 1: Ceria CMP results

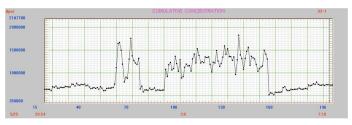

The AccuSizer Mini generates the highest accuracy and resolution results quickly, and at count rates higher than any other technology. This creates LPC and tail results with the best statistical accuracy — detecting the few large particles that will hurt your yield rates, see Figure 2 below with LPC concentration levels near 1 million/mL during a pump failure.

*Fig. 2: LPC vs. time online AccuSizer results*

> Have a click on this <u>video</u> to discover the AccuSizer

### **Feedback**

We value your feedback and suggestions to help us improve Zero Defects. Please send your questions, suggestions and comments to <u>europe.region@entegris.com</u> If you would like more information regarding Entegris products and services, please contact your customer service centers (page 1) or refer to Entegris online at <u>www.entegris.com</u>

| ZERO DEFECTS ENTEGRIS NEWSLETTER |       | <b>Free subscription Form</b><br>email to <b>europe.region@entegris.com</b><br>fax to +33 (0)4 76 35 73 80 |                                                |

|----------------------------------|-------|------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Name*:                           |       | Job title*:                                                                                                |                                                |

| Company name*:                   |       |                                                                                                            | _ Dept:                                        |

| Address:                         |       |                                                                                                            |                                                |

| Postal code:                     | City: |                                                                                                            | Country:                                       |

| Tel. :                           |       |                                                                                                            | Send me the Zero Defects pdf file $\Box$       |

| E-mail*:                         |       |                                                                                                            | Send me the direct link of Zero Defects $\Box$ |

| * required to complete           |       |                                                                                                            |                                                |

Entegris<sup>®</sup>, the Entegris Rings Design<sup>®</sup>, and other product names are trademarks of Entegris, Inc. as listed on **entegris.com/trademarks**. All third-party product names, logos, and company names are trademarks or registered trademarks of their respective owners. Use of them does not imply any affiliation, sponsorship, or endorsement by the trademark owner. ©2018 Entegris, Inc. | All rights reserved. | Printed in the USA | 9000-10080ENT-0718