# Optimizing Wafer Polishing: Innovations in CMP Techniques and Filtration

Chloe (Ting-Chen) Chen, Jason (Yu-Chieh) Fu, Conway Chen, Nathan Hou, Nate Chang, Elaine Wu, Alex Chuang – Entegris, Inc.

# **ABSTRACT**

This study focuses on significant advancements in the chemical mechanical polishing (CMP) process aiming to reduce common defects through the implementation of effective filtration solutions. Utilizing a 3 wt% silica slurry, we systematically evaluated the impact of Entegris nano melt-blown (NMB) filters on improving polishing efficiency and stability. The design of experiments (DOE) methodology allowed us to explore and optimize multiple variables, assessing the performance of the silica slurry under accelerated aging conditions and monitoring key factors such

as conductivity and temperature changes. Our findings demonstrated that the use of NMB filters effectively stabilized large particle count (LPC) levels, achieving approximately 95% retention for particles >0.43 µm and significantly reducing total scratch defects to less than 10%. The comprehensive batch and point-of-use (POU) filtration solutions presented in this study are crucial for enhancing wafer quality and yield, thereby advancing semiconductor manufacturing processes.

# INTRODUCTION

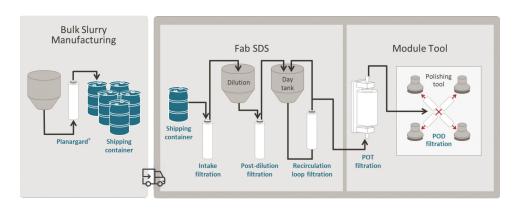

Semiconductor manufacturing relies heavily on precise control and refinement of processes like CMP, which is crucial for achieving the stringent surface flatness and quality demanded by advanced semiconductor devices. As technology advances and process dimensions shrink, the challenges associated with CMP become increasingly intricate (Figure 1). There is a growing demand for enhanced process stability and efficiency, driven by the continuous evolution of CMP technologies. To address the complexity of optimizing CMP processes, particularly with

silica-type slurries, this study focuses on leveraging the DOE methodology. DOE offers a systematic approach to explore and optimize multiple variables concurrently, facilitating the identification of optimal process conditions. Specifically, this research delves into the application of DOE in filtration testing of silica slurries. Filtration tests serve as a critical step in assessing slurry quality and consistency by evaluating factors like filtration efficiency and particle retention under controlled conditions. The insights gained from these experiments are instrumental

in improving polishing performance, reducing defects, and ultimately enhancing the overall quality and yield of semiconductor wafers.

Figure 1. General CMP filtration process.

# **EXPERIMENTAL**

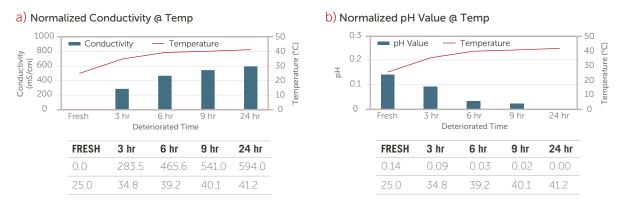

This study focuses on simulating the challenges and solutions encountered during the final stages of the CMP process. Prior to designing the DOE, pre-cycling tests were conducted using a 3 wt% silica slurry to collect data on conductivity, pH impacts, and temperature variations (Figure 2).

Figure 2. a) Conductivity and temperature; b) pH shock and temperature.

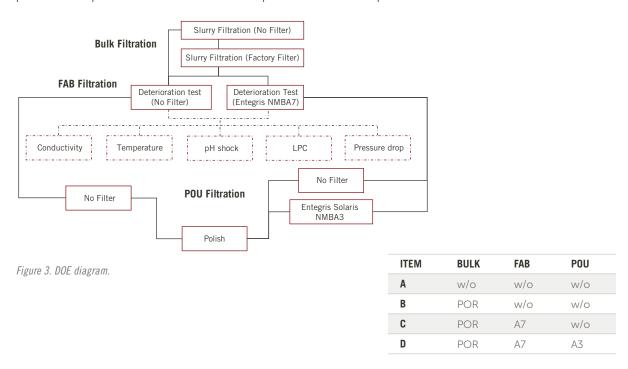

Our observations indicated that while pH changes were negligible, both temperature and conductivity exhibited slight variations, with higher temperatures correlating with increased conductivity. These preliminary tests helped us gather baseline data essential for the subsequent DOE (Figure 3). In the DOE plan, Entegris NMB filters with various pore sizes were utilized to improve polishing outcomes. LPC was analyzed using the Entegris AccuSizer A9000 FX Nano AD system, focusing on the retention efficiency of particles in the  $\sim$ 0.2 – 0.4  $\mu$ m range. The total defect counts on polished wafers were determined using the KLA-Tencor Surfscan® SP7, which was scanned by 40 nm and 50 nm threshold with edge exclusion 3 mm. Additionally, wafer defect reviews were conducted using the AMAT G7 to provide a comprehensive assessment of the impact of different DOE parameters on defect distribution.

# **RESULTS AND DISCUSSION**

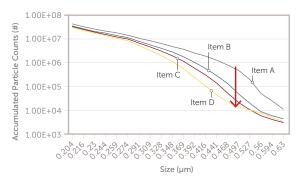

First, let's observe the LPC results changes between DOE items. We divided LPC into different particle size counts and retention to discuss. For LPC test result (Figure 4), Item A exhibited a significantly higher LPC than Items B, C, and D.

# Different Particle Size Counts

Figure 4. Different particle size counts LPC.

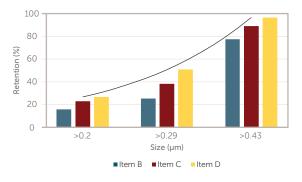

For the retention efficiency (Figure 5), the retention efficiency of particles in different DOE items varied considerably. Item D showed approximately 95% retention for particles >0.43 µm, followed by Item C with about 85% and Item B with around 80%. These results demonstrate the efficacy of the NMB filters in reducing LPC.

# LPC Retention

Figure 5. Different particle size counts LPC.

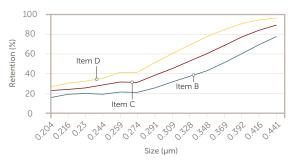

The comparison of particle size and retention (Figure 6) indicates significant differences among the DOE items, with Item D showing the best retention performance, followed by Items C and B. This highlights the importance of choosing the right filtration parameters to maximize retention efficiency.

### LPC Removal Trend (Retention vs. Size)

Figure 6. Particle size and retention.

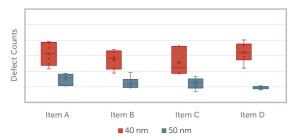

For the wafer data, the total de-fect counts for 40 nm and 50 nm particles were analyzed using the KLA-Tencor Surfscan SP7. While the changes at 40 nm were minimal, significant reductions were observed at 50 nm, indicating that larger particles are more effectively captured and reduced through optimized filtration (Figure 7).

# Total Defect @ SP7

Figure 7. The DOE 40 nm and 50 nm total defect result @KLA-Tencor Surfscan® SP7.

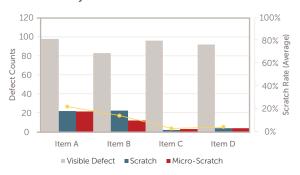

The SEM defect analysis confirmed that different stages of filtration could reduce overall scratch defects to less than 10% (Figure 8). This result underscores the effectiveness of the NMB filters in minimizing surface defects during the CMP process.

The DOE results illustrate the critical role of effective filtration in the CMP process. By optimizing filtration parameters, we can achieve a significant reduction in LPC and surface defects, leading to improved wafer quality and yield.

# TEOS Defect by AMATG7

Figure 8. TEOS defect review @AMAT G7.

### CONCLUSIONS

The implementation of Entegris NMB filters is a crucial advancement in the CMP process, offering significant improvements in wafer polishing efficiency and defect reduction. Through systematic DOE enhanced filtration testing, our study demonstrates that NMB filters can effectively stabilize LPC levels, achieving around 95% retention at >0.43 µm. This substantial retention capability directly correlates with a marked decrease in overall scratch defects to less than 10%, particularly for particles at 50 nm. These results underscore the pivotal role of NMB filters in optimizing CMP processes, thereby enhancing wafer quality, yield, and device reliability. The adoption of NMB filters is poised to drive forward advancements in semiconductor manufacturing, ensuring higher performance and onsistency in production outcomes.

# **ACKNOWLEDGMENTS**

Thanks to our colleagues at Entegris for their continuous support and collaboration throughout this study. Their contributions were instrumental in the successful completion of this research.

This was first presented at the 2024 ICPT conference.

### FOR MORE INFORMATION

Please call your Regional Customer Service Center today to learn what Entegris can do for you. Visit <a href="mailto:entegris.com">entegris.com</a> and select the <a href="mailto:Contact Us">Contact Us</a> link to find the customer service center nearest you.

# TERMS AND CONDITIONS OF SALE

All purchases are subject to Entegris' Terms and Conditions of Sale. To view and print this information, visit <u>entegris.com</u> and select the <u>Terms & Conditions</u> link in the footer.

Corporate Headquarters 129 Concord Road Billerica, MA 01821 USA

Customer Service

Tel +1 952 556 4181

Fax +1 952 556 8022 Toll Free 800 394 4083

Entegris®, the Entegris Rings Design®, and other product names are trademarks of Entegris, Inc. as listed on entegris.com/trademarks. All third-party product names, logos, and company names are trademarks or registered trademarks of their respective owners. Use of them does not imply any affiliation, sponsorship, or endorsement by the trademark owner.