可能性の探求:デバイスのスケーリングに対する、製造プロセスに使用される材料からの包括的アプローチ

フットプリントの縮小化と高度な演算能力への要求がこれまでになく高まり、電力消費を抑えながらより高速に動作するトランジスターが求められています。しかし、この目標を念頭に置いて開発された新しい材料やアーキテクチャーを、研究開発 (R&D) から本格的な大量生産へ移行するのは容易なことではありません。複雑な幾何学的構造を持つ先端ノードの半導体デバイスの製造は、3D構造、高アスペクト比、ナノスケールの寸法など多くの課題があります。最終的に、デバイスメーカーが高性能、高歩留まり、低コストを同時に達成するための変革をいかに速くできるかが成功の鍵を握っています。しかし、これは単独で達成できるものではなく、サプライチェーンと半導体のエコシステム全体にわたる強力なパートナーシップが必要です。

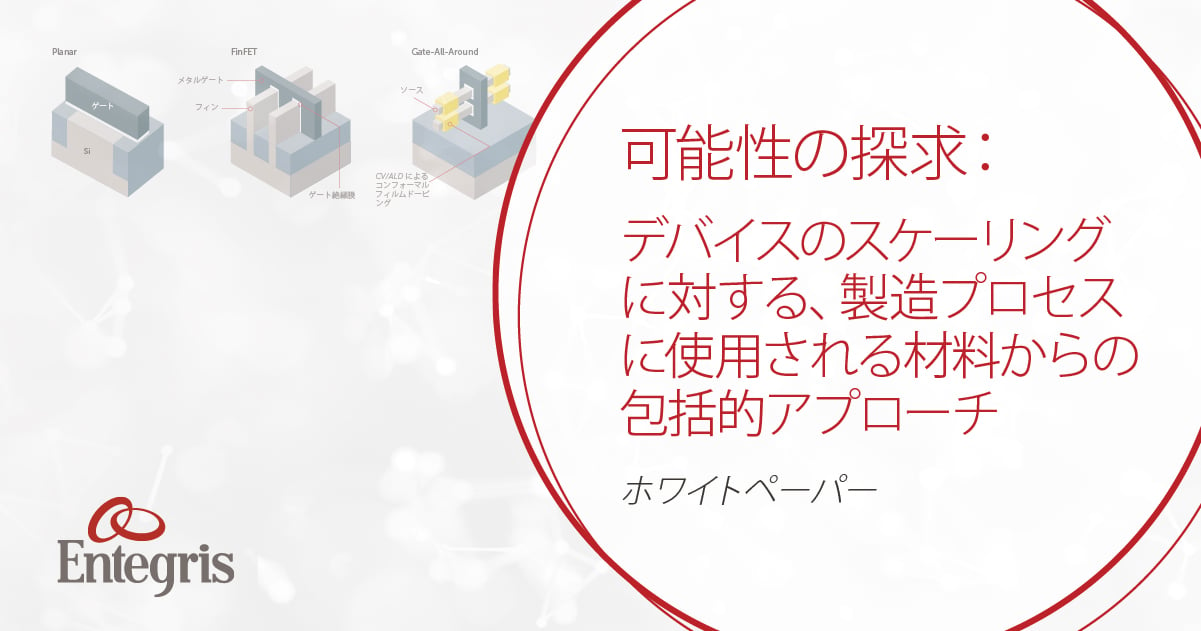

業界が 7 nm のプロセスノードを超えて進歩するにつれ、生産目標を達成するためにデバイスアーキテクチャー、仕様寸法、プロセス材料、製造装置の変更が必要となります。ただし、製造シーケンスの一部の課題を解決するための材料とプロセスの変更は、以降の製造工程にも変更が必要になることがあります。したがって、半導体デバイスメーカーは、金属からエッチング液に至るまで、すべてのサプライヤーと緊密に連携し、要求の厳しい材料や複雑な幾何学的な制約のあるアーキテクチャーへの移行におけるすべての影響を十分に理解する必要があります。デバイスの小型化に関する問題は、メモリとロジック両方のデバイスに当てはまります。

このホワイトペーパーは、7 nm 超のプロセスノードの進歩に伴う、ロジックデバイスのスケーリングの問題と生産目標を達成するためのデバイスアーキテクチャ、仕様寸法、プロセス材料、製造装置の変更の必要性について説明しています。